# USING TRLS AND SYSTEM ARCHITECTURE TO ESTIMATE TECHNOLOGY INTEGRATION RISK

Garg, Tushar; Eppinger, Steven; Joglekar, Nitin; Olechowski, Alison Massachusetts Institute of Technology, United States of America

#### Abstract

Risk estimation is a key activity for product development and technology integration programs. There are a number of decision support tools that help project managers identify and mitigate risks in a project, however few explicitly consider the effects of architecture on risk. We propose a novel risk estimation framework that includes considerations of the system architecture. By starting with traditional project management literature, we define risk as a combination of likelihood and impact. We use Technology Readiness Levels as our measure for likelihood, and given that change propagates through interfaces, we used measures that relate to connectivity to estimate impact. This framework is applied to an industry example and we visualize the data in different formats to aid in analysis. The insights gained from this analysis are discussed, and we conclude that the risk estimation framework provides estimates that are in line with the experience of engineers at the company.

Keywords: Risk management, Uncertainty, New product development, Systems Engineering (SE), Project management

#### **Contact**: Tushar Garg Massachusetts Institute of Technology System Design and Management United States of America tgarg.sfo@gmail.com

Please cite this paper as:

Surnames, Initials: *Title of paper*. In: Proceedings of the 21<sup>st</sup> International Conference on Engineering Design (ICED17), Vol. 3: Product, Services and Systems Design, Vancouver, Canada, 21.-25.08.2017.

### **1** INTRODUCTION

One of the key activities in new product development (NPD) programs is the measurement of risk. Risk is defined by the PMBOK (Project Management Body of Knowledge) as "an uncertain event or condition that, if it occurs, has an effect on at least one project objective" (Project Management Institute, 2008). For project managers, the main concerns are cost, schedule and scope. Improper or insufficient risk identification practices can result in unanticipated schedule overruns, significant rework, budget inflation, and a reduced capability for delivering the chartered scope of the project.

In this work, we propose a practical risk identification tool to be used by engineers and technical managers on projects involving integration of new technology components into systems. Our framework combines system architecture concepts and analysis with technology readiness levels (TRLs) to focus attention on high-risk components and interfaces. Of the four risk categories identified by Project Management Institute (2008), our work addresses technical risk, which deals with the uncertainty related to developing and integrating new or complex technologies. Project, organizational and external risks are not discussed in this research.

# 2 LITERATURE CRITIQUE

There is substantial literature available on risk management and related decision support frameworks. Some of these frameworks have been applied widely in industrial practice, and others are proposals within the academic sphere. Our work relies heavily on the concept of system architecture, defined by Crawley et al. (2015) as "an abstract description of the entities of a system and the relationships between those entities" with the relationships referenced as interfaces within this text. Because of our focus, we selected works from three streams of research: papers that measured technology integration risk directly and explicitly considered architecture and papers that relate to TRLs. We start by examining each of these frameworks and their contribution, followed by a table summary and comparison.

One of the most widely used methods for managing risk for NPD programs is the Technology Readiness Assessment (TRA) that has been established by NASA. TRA is a process used to systematically assess the maturity of technologies using a nine point scale called the Technology Readiness Levels (TRL) (ASDRE, 2011). In assessing the TRL of any given technology, a practitioner must ask questions related to the demonstrated functionality, integration completeness, test environment and fidelity, with the highest TRL representing a technology that has been "flight proven" through actual operation on a real mission in the target environment. Results from this practice are encouraging: a study of 62 United States Department of Defense development and acquisition programs found that those that started with all components at a TRL of 7 or higher finished nearly on time and within budget, however those that started with TRLs lower than 7 experienced an average 32% development cost growth from first estimate and large schedule delays (United States Government Accountability Office, 2007). This points to the usefulness of TRLs as a measure of uncertainty in NPD programs. Since its introduction in the 1970s, the TRA methodology has spread beyond the defense context to other complex engineering industries such as automotive, oil and gas, semiconductor, and healthcare.

While the TRA has undoubtedly proven its usefulness, it is not without its drawbacks. Many of the challenges with TRA have been documented by Olechowski et al. (2015), but the point most salient to this discussion is the challenge of "integration and connectivity". While TRLs are primarily evaluated on a component level, any engineering manager can attest that interfaces need to be taken into account to properly evaluate technology readiness and the TRL definitions do not provide sufficient guidance on this point.

Sauser et al. (2010) have attempted to address this by introducing Integration Readiness Levels (IRLs) to be evaluated in addition to TRLs. Explicit assessment of integration readiness gives project managers more data points in the decision making process, however the assessment itself can be costly, especially considering that each component is likely to have many interfaces. Jimenez and Mavris, (2014) have pointed out that the IRL scale was developed from the OSI (Open Systems Interconnection) Seven Layer Networking model, a model used to characterize communications in a computing context, which may not have meaningful applications outside of computer networking topics. As an alternative, Jimenez and Mavris, (2014) have proposed a slightly different approach where integration readiness is considered a sub-attribute of technology readiness, instead of its own distinct scale. This approach benefits from simplicity as a single common language for communicating technology readiness is preserved.

Both of these approaches add information about direct component-to-component interfaces in exchange for a higher assessment effort. These approaches do not, however, address the effects of interfaces beyond the direct connections to the evaluated components. One can imagine a scenario where two components have the same number of interfaces, but one is located in a central area within the architecture, and the other is more isolated. The former is more likely to propagate change through to the whole system. In this paper, we refer to connections beyond the first-degree interfaces as indirect interfaces.

Brady (2002) proposed a framework that combined technology readiness levels and a measure of interface strength between components to calculate risk values for interfaces in a product. Technology readiness levels were assessed for each component, and this scale was mapped to a Technology Risk Factor (TRF) scale between 1 and 5 with the highest risk value corresponding with the lowest readiness level. The system architecture was displayed in a matrix with each cell representing an interface between two components. The value for this cell was calculated by taking the product of the TRF of each component and the interface strength. High valued cells were considered to be high risk. Brady's approach benefits from considering direct interfaces when assessing risk, however this requires an assessment of interface strength for each interface in addition to TRLs for each component, so we consider this to be a high effort method.

Clarkson et al. (2004) developed a method which assesses the likelihood of change propagation and combined that with the impact to obtain a risk matrix for the system. This method does not account for TRLs. Instead, it requires practitioners to make two assessments for each pair of components that share an interface: the likelihood that one component will propagate a change to the other, and the impact of that change on the receiving component. This assessment is based on the experience of engineers and documentation from past projects and, as a result of the sheer quantity of assessments, can be effort intensive. Once these assessments are made, the practitioner calculates "combined likelihood" and "combined impact" scores that include the effects from all possible change propagation paths between two components. This is accomplished by generating change propagation trees and summing up values from each path, weighted by length. This technique has the advantage of taking into account direct and indirect interfaces, and our framework seeks to achieve similar results with a lower effort.

We have summarized the papers referenced above in Table 1 for ease of comparison. This table is organized according to the two types of papers: risk with architecture and technology readiness levels. Furthermore, we have decided to examine each paper through three different lenses: whether or not they address technology integration risk, the assessment level of effort, and whether or not interfaces are considered as part of the analysis. Finally, we have highlighted cells within the matrix that most closely match the framework that we propose in this paper.

|                                             | Technolog                                                             | gy Readiness Levels & D                                                           | Risk with Architecture                                                                                   |                                                                                                               |                                                                                                                                                |  |  |  |  |

|---------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| COMPARISON<br>FACTOR                        | NASA TRLs                                                             | Sauser et al. (2010)                                                              | Jimenez and Mavris<br>(2014)                                                                             | Brady (2002)                                                                                                  | Clarkson et al. (2001)                                                                                                                         |  |  |  |  |

| Addresses<br>Technology<br>Integration Risk | Used in risk<br>management, but<br>does not claim to<br>measure risk. | Proposes another<br>assessment in<br>addition to TRLs for<br>integration risk.    | Extends the<br>assessment of TRLs<br>but does not claim to<br>measure risk directly.                     | Views risk as a<br>combination of a 1-5<br>TRL mapped scale<br>and an assessment of<br>interface strength.    | Views risk as a<br>combination of<br>likelihood and impact.<br>Measures likelihood<br>and impact from past<br>experience and<br>documentation. |  |  |  |  |

| Assessment Effort<br>Level                  | LOW TRL is<br>assessed for each<br>component.                         | MED Requires IRLs<br>to be assessed for<br>each component in<br>addition to TRLs. | MED Requires TRL<br>to be assessed for<br>each component,<br>with added effort to<br>address interfaces. | HIGH Requires TRLs<br>to be assessed for<br>every component,<br>and interface strength<br>for each interface. | HIGH Requires<br>likelihood and impact<br>to be evaluated for<br>each interface, in<br>both directions.                                        |  |  |  |  |

| Interfaces Are<br>Considered                | Interfaces are only<br>considered for higher<br>TRLs (6-9).           | Direct interfaces are<br>considered as part of<br>the additional<br>assessment.   | Direct interfaces are<br>considered as an<br>additional sub<br>attribute of TRLs.                        | Only direct interfaces<br>are considered.                                                                     | Direct and indirect<br>interfaces are<br>considered.                                                                                           |  |  |  |  |

#### Table 1. Comparison matrix of selected literature

In summary, our research seeks to address some of the challenges of the previously mentioned works, namely: how can we estimate technology integration risk using concepts of technical maturity, architecture, and connectivity, while keeping assessment effort low enough to allow for practical application within industry? We use the next section to explain our proposal and the mechanics behind its application.

#### **3 OUR METHOD**

When defining technology integration risk, we choose to focus on the concepts of engineering change and change propagation. For highly complex systems, engineering change is required to address mistakes during the design process due to uncertainty. In some cases, those changes propagate through interfaces to other components in the system. When mismanaged, relatively small changes can propagate into a cascade of changes that sweep across the system, incurring significant costs and rework (Terwiesch and Loch, 1999). Thus, we start our definition by asserting that the technology integration risk of each component i is estimated using a common risk metric -- the product of likelihood and impact as seen in Equation 1 (Project Management Institute, 2008).

$$Risk_i = L_i \cdot I_i \tag{1}$$

$L_i$  is the likelihood that the component technology requires a change to fulfil its function. This is estimated through the use of TRLs, which have been shown to be good estimators of uncertainty in the technology integration process (United States Government Accountability Office, 2007).

$I_i$  is the severity of impact if the component is forced to change. We examine the overall architecture and the component interfaces in particular to estimate the impact through the context of change propagation.

In the following sections, we describe the rationale and method behind the inputs for our risk calculation. Given that some of our inputs are unbounded scales, we choose to calculate relative risk rather than absolute risk by rescaling all of our inputs to fall between the ranges of 1-10. We choose 1-10 for our range as this is the standard chosen for FMEA analysis (Segismundo and Miguel, 2008).

#### A. Likelihood of change

There is a relationship between the likelihood of technical or integration problems in design and the degree of certainty that we have about the design, implementation, and capabilities of a particular component or technology. As we design, test, iterate, and integrate the product or system, we drive uncertainty out through a range of validation activities. In order to utilize this concept of uncertainty in our calculation of risk, we need to find a way to measure it. Fortunately, NASA's TRL scale offers us exactly what we are looking for: a well-documented and widely used scale for measuring the degree of maturity in a given component. After examination, it is easy to see that maturity is also an indicator for uncertainty. Highly mature components, those that have been well tested and proven in relevant environments, have low uncertainty levels. That is precisely the purpose of integration and testing – to drive out uncertainty within the system. Thus, we choose the TRL scale as our measurement of uncertainty. The full TRL scale is presented in Table 2.

# Table 2. Summary of Technology Readiness Levels (NASA Office of the Chief Engineer, 2013)

| TRL | Definition                                                                               |

|-----|------------------------------------------------------------------------------------------|

| 9   | Actual system "flight proven" through successful mission operations                      |

| 8   | Actual system completed and "flight qualified" through test and demonstration (ground or |

|     | flight)                                                                                  |

| 7   | System prototype demonstration in a target/space environment                             |

| 6   | System/subsystem model or prototype demonstration in a relevant environment (ground or   |

|     | space)                                                                                   |

| 5   | Component and/or breadboard validation in relevant environment                           |

| 4   | Component and/or breadboard validation in laboratory environment                         |

| 3   | Analytical and experimental critical function and/or characteristic proof-of-concept     |

| 2   | Technology concept and/or application formulated                                         |

| 1   | Basic principles observed and reported                                                   |

Considerable literature exists on the processes and guidelines for assessing TRLs, and as such we will not detail the specifics here. For our analysis, we evaluate each component within the system on this 1-9 TRL scale to get our base likelihood score. Since a TRL of 9 corresponds to the lowest possible uncertainty, and thus lowest likelihood of risks manifesting, we decided to invert this scale by making a TRL of 9 correspond to a likelihood value of 1, and a TRL of 1 to a likelihood value of 9. This produces a vector where the highest value corresponds to the highest likelihood of risks manifesting. Finally, as mentioned at the beginning of this section, we rescale the vector linearly such that the range falls between 1-10.

#### B. Severity of impact

When presented with a specific engineering change, a panel of experienced engineers can provide a rough magnitude estimate of the system impact with relative ease. However, without a specific change instance, it can be difficult to conceive of how impactful future changes to any particular component could be. One way to approach this problem is to estimate the potential for a component to propagate change. Change propagation should be closely monitored in development programs as it can lead to unanticipated impacts to costs and schedule. We know from Clarkson et al. (2004) that change propagates between components through their interfaces. Thus, when trying to estimate the potential impact on the overall system, it is reasonable to consider the system architecture, and specifically, the connectivity of each component.

Given that change propagates through interfaces, we propose that components with higher connectivity are more likely to spread change within the system. With this assumption, we have a number of tools at our disposal for estimating severity of impact. We can analyze the system architecture by representing it as an undirected network where components are represented as nodes, and interfaces are represented as edges between nodes. With this view, one of the simplest methods for estimating severity of impact would be to count the number of interfaces for each component. In network terms, this would be referring to the nodal degree of the components. After rescaling the degree count for each node to fall between 1-10, we obtain a vector of severity scores for each component which is multiplied by our likelihood vector to obtain a risk score for each component. The key advantage to using this method is the ease of calculation. Engineers will be able to compute this risk score for their system with simple tools like Microsoft Excel and they can immediately reap the insights.

While nodal degree is a simple measure that can be applied for this analysis, it does not take into account architectural characteristics beyond the immediate interfaces of the component. In some cases, a measure that accounts for more indirect change propagation paths could be more useful. Graph theory offers us network centrality measures that aim to take into account these architectural attributes, and in this work we considered the following alternatives to degree:

- Closeness centrality the average distance from all of the other nodes in the network, only taking into account geodesics, or shortest paths (Borgatti, 2005).

- Betweenness centrality the proportion of geodesics that pass through any given node (Borgatti, 2005).

- Information centrality Similar to betweenness, however it includes and penalizes paths other than the geodesics (Estrada et al., 2010).

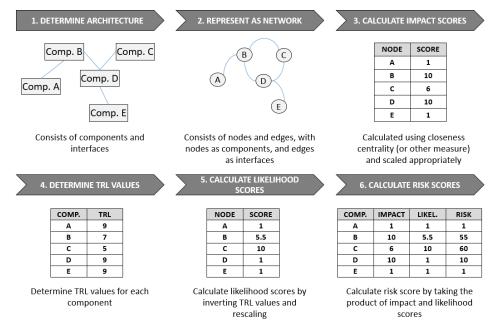

As with our degree measure, we rescale each of these measures for consistency. Each measure provides a unique perspective on the importance of nodes in a network, however it is important to note that they are all highly correlated and in most cases degree will net similar insights to the other measures. Still, on occasion there will be some nodes where the different measures have significant differences, and generally these nodes have some unique characteristics that are worth examining. Calculating the three centrality measures generally requires specialized software which, while freely available, may be less accessible and more difficult to understand. It is up to the practitioner of this method to decide which centrality measure is most meaningful for their application. Further analysis and a discussion of strengths and weaknesses of different centrality measures can be found in Garg's (2017) master's thesis. The overall method that we apply in this research is illustrated and summarized in Figure 1.

Figure 1. Summary of risk calculation method

#### 4 INDUSTRY APPLICATION

To develop and refine our framework, we worked with Analog Devices Inc. as our industry partner for this study. Analog Devices is a large multinational semiconductor company headquartered in Massachusetts. We worked with them to analyze a NPD program that is currently underway. The team was working on developing a new sensor package that could be used to precisely measure angular position. We worked with the team to gather the following inputs:

• A decomposition of the system into 6 subsystems and 20 components.

• A list of the interfaces between every component in the system.

• A TRL assessment for every component in the system.

These data were used to build a view of the system architecture and develop a network representation of the system as illustrated in steps (1) and (2) from Figure 1. Once we had collected all of the data we calculated our impact and likelihood vectors as in steps (3), (4) and (5) of Figure 1 to obtain our final risk scores (step 6). For simplicity's sake, we demonstrate this example using nodal degree as our measure for impact. The inputs and final risk calculation is shown in Figure 2 with bars in each cell to represent the magnitudes.

|           |                                      |   | ikelihood         | lr     | Risk              |      |

|-----------|--------------------------------------|---|-------------------|--------|-------------------|------|

| Subsystem |                                      |   | <b>Risk Input</b> | Degree | <b>Risk Input</b> | RISK |

|           | Die attach                           | 8 | 2.5               | 13     | 10.0              | 25   |

| Package   | Leadframe                            | 7 | 4                 | 5      | 2.8               | 11.2 |

| Fackage   | Wirebond                             | 9 | 1                 | 6      | 3.7               | 3.7  |

|           | Plastic Mold                         | 9 | 1                 | 13     | 10.0              | 10   |

|           | Sensor 1 Analog Front End            | 7 | 4                 | 4      | 1.9               | 7.6  |

| ASIC for  | Sensor 1 Analog to Digital Converter | 3 | 10                | 5      | 2.8               | 28   |

| Sensor 1  | Sensor 1 Calibration                 |   | 1                 | 5      | 2.8               | 2.8  |

|           | Sensor 1 Processor                   | 9 | 1                 | 5      | 2.8               | 2.8  |

|           | Sensor 2 Analog Front End            | 9 | 1                 | 4      | 1.9               | 1.9  |

| ASIC for  | Sensor 2 Analog to Digital Converter | 3 | 10                | 5      | 2.8               | 28   |

| Sensor 2  | Sensor 2 Calibration                 | 9 | 1                 | 3      | 1.0               | 1    |

|           | Sensor 2 Processor                   | 9 | 1                 | 5      | 2.8               | 2.8  |

|           | ASIC Input/Output                    | 9 | 1                 | 6      | 3.7               | 3.7  |

|           | ASIC Non-volatile Memory             | 6 | 5.5               | 7      | 4.6               | 25.3 |

| ASIC      | ASIC Regulator                       | 9 | 1                 | 7      | 4.6               | 4.6  |

| ASIC      | ASIC Oscillator                      | 9 | 1                 | 10     | 7.3               | 7.3  |

|           | ASIC Analog Front End                | 9 | 1                 | 4      | 1.9               | 1.9  |

|           | ASIC Analog to Digital Converter     | 9 | 1                 | 6      | 3.7               | 3.7  |

| Sensor 1  | Sensor 1 Design/layout               | 5 | 7                 | 7      | 4.6               | 32.2 |

| Sensor 2  | Sensor 2 Design/layout               | 5 | 7                 | 6      | 3.7               | 25.9 |

Figure 2. Vector representation of the components and their scores

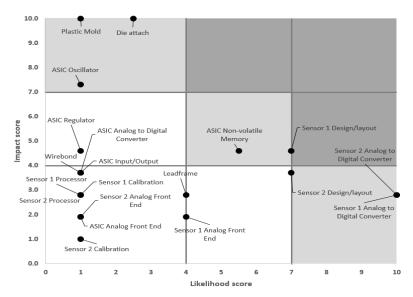

To better visualize the risk scores, we can graph the data on a scatter plot as in Figure 3, with the two axis corresponding to likelihood and severity. This view has been widely utilized in risk management literature, and most practitioners are familiar with the interpretation of this view (Project Management Institute, 2008). The graph is divided into a grid that allow managers to visualize the different types of risks for their program. Components in the top left area have high impact scores, but low likelihood scores, and thus have moderate risk. Components in the bottom right have low impact scores, but high likelihood scores, and while they also have moderate risk, managers may choose to use different risk mitigation strategies for these two categories. While this view is excellent for visualizing risk on the component level, it doesn't provide information about the specific interfaces that each component has. With the interface information, researchers and practitioners are better able to interrogate the results and understand the underlying reasons for the specific assessment.

Figure 3. Two-axis view of likelihood and impact

In an effort to preserve information about interfaces, we combine the risk score information with a Design Structure Matrix (DSM) view of the system (Eppinger and Browning, 2012). To do this, we choose each off-diagonal mark in the matrix to represent a risk score composed of the two interfacing components. The calculation is done according to Equation 2:

$$Interface \ risk_{ij} = \ max(L_i, L_j) \cdot max(I_i, I_j)$$

(2)

Where  $L_i$  and  $L_j$  represent the likelihood scores for the two interfacing components;  $I_i$  and  $I_j$  represent the impact scores for each component. We can see the intuition behind this choice in the following example: suppose a highly uncertain (low TRL) component were to interface with a highly connected (high impact) component. If the high uncertainty component were forced to change during the design process, it is possible that the highly-connected component would require a change as well, and it may take careful design and planning to ensure that the change does not propagate beyond that component. Indeed, it may not be possible to fully contain the changes at this highly connected component, and thus you can see the need for careful scrutiny of that interface. Figure 4 allows us to see the results of this analysis. We leave the component-level risk calculations as a vector in the "risk" column as an additional reference.

| Subsystem            | COMPONENT                            | RISK | TRL | 8   | 7  | 9  | 9   | 7  | 3   | 9  | 9  | 9  | 3   | 9  | 9  | 9  | 6  | 9  | 9  | 9  | 9  | 5  | 5  |

|----------------------|--------------------------------------|------|-----|-----|----|----|-----|----|-----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|

| Package              | Die attach                           | 25   | 8   | -   | 40 | 25 | 25  | 40 | 100 |    |    | 25 | 100 |    |    |    |    | 25 | 25 | 25 | 25 | 70 | 70 |

|                      | Leadframe                            | 11   | 7   | 40  |    | 15 | 40  |    |     |    |    |    |     |    |    |    |    |    |    |    |    | 32 | 26 |

|                      | Wirebond                             | 4    | 9   | 25  | 15 |    | 10  |    |     |    |    |    |     |    |    | 4  |    |    |    |    |    | 32 | 26 |

|                      | Plastic Mold                         | 10   | 9   | 25  | 40 | 10 |     | 40 | 100 |    |    | 10 | 100 |    |    |    |    | 10 | 10 | 10 | 10 | 70 | 70 |

| ASIC for<br>Sensor 1 | Sensor 1 Analog Front End            | 8    | 7   | 40  |    |    | 40  |    | 28  |    |    |    |     |    |    |    |    |    |    |    |    | 32 |    |

|                      | Sensor 1 Analog to Digital Converter | 28   | 3   | 100 |    |    | 100 | 28 |     | 28 |    |    |     |    |    |    |    |    | 73 |    |    |    |    |

|                      | Sensor 1 Calibration                 | 3    | 9   |     |    |    |     |    | 28  |    | 3  |    |     |    |    |    | 25 |    |    |    | 4  | 32 |    |

|                      | Sensor 1 Processor                   | 3    | 9   |     |    |    |     |    |     | 3  |    |    |     |    |    | 4  | 25 |    | 7  |    |    | 32 |    |

| ASIC for<br>Sensor 2 | Sensor 2 Analog Front End            | 2    | 9   | 25  |    |    | 10  |    |     |    |    |    | 28  |    |    |    |    |    |    |    |    |    | 26 |

|                      | Sensor 2 Analog to Digital Converter | 28   | 3   | 100 |    |    | 100 |    |     |    |    | 28 |     | 28 |    |    |    |    | 73 |    |    |    |    |

|                      | Sensor 2 Calibration                 | 1    | 9   |     |    |    |     |    |     |    |    |    | 28  |    | 3  |    | 25 |    |    |    |    |    |    |

|                      | Sensor 2 Processor                   | 3    | 9   |     |    |    |     |    |     |    |    |    |     | 3  |    | 4  | 25 |    | 7  |    |    |    | 26 |

|                      | Input/Output                         | 4    | 9   |     |    | 4  |     |    |     |    | 4  |    |     |    | 4  |    | 25 | 5  | 7  |    |    |    |    |

|                      | Non-volatile Memory                  | 25   | 6   |     |    |    |     |    |     | 25 | 25 |    |     | 25 | 25 | 25 |    | 25 | 40 |    |    |    |    |

| ASIC                 | Regulator                            | 5    | 9   | 25  |    |    | 10  |    |     |    |    |    |     |    |    | 5  | 25 |    | 7  | 5  | 5  |    |    |

|                      | Oscillator                           | 7    | 9   | 25  |    |    | 10  |    | 73  |    | 7  |    | 73  |    | 7  | 7  | 40 | 7  |    |    | 7  |    |    |

|                      | Analog Front End                     | 2    | 9   | 25  |    |    | 10  |    |     |    |    |    |     |    |    |    |    | 5  |    |    | 4  |    |    |

|                      | Analog to Digital Converter          | 4    | 9   | 25  |    |    | 10  |    |     | 4  |    |    |     |    |    |    |    | 5  | 7  | 4  |    |    |    |

| Sensor 1             | Sensor 1 Design/layout               | 32   | 5   | 70  | 32 | 32 | 70  | 32 |     | 32 | 32 |    |     |    |    |    |    |    |    |    |    |    |    |

| Sensor 2             | Sensor 2 Design/layout               | 26   | 5   | 70  | 26 | 26 | 70  |    |     |    |    | 26 |     |    | 26 |    |    |    |    |    |    |    |    |

Figure 4. DSM view of the system risk

# 5 DISCUSSION

We presented the findings from the figures above to the team at Analog Devices and discussed the results. Our analysis suggests that the riskiest components were both of the sensors, Sensor 1 and Sensor 2, followed by the analog to digital converters for both sensors. This aligned well with the experience and expectations of the Analog Devices team. In addition, the analysis shows that the die attach portion of the packaging subsystem is risky. In the early phases of the data collection, the managers had mentioned that the packaging was a point of concern for them, and this is seen in the risk of the die attach.

One manager remarked that the team at Analog Devices implicitly does this kind of a risk assessment in their head when asked to gauge the risk level of various components in their program. The engineer would think about how "new" or uncertain a component was, how central of a role it played in the system, and use these two ideas to come up with an estimate for risk. The manager pointed out that this method formalizes that thought process onto paper by making it measured and objective.

Another point that came up during discussion was regarding the ability for TRL alone to capture the uncertainty or risk likelihood of a component. A manager pointed out that there are scenarios where two components are listed at a TRL of 5, however the project team has less confidence in the ability of the

engineering team to achieve the requisite TRL level of 9 for one of the component than for the other. The example that was given was for components utilizing a new semiconductor process. Even if these new components have been demonstrated in a lab setting, it is still possible that process will never mature to the required quality and reliability targets, and thus there is significant uncertainty in the progression of that component. This can be contrasted with another component like an analog to digital converter using an older, more mature process. It is possible that this particular circuit element has never been built before and it has only been demonstrated in a lab environment, however the team has confidence that it will reach a TRL of 9 because the process is highly mature.

This topic has been discussed by Olechowski et al. (2015) as the concept of "confidence to progress". Technology Readiness Levels do not include any measure of the confidence that the engineering team has to progress to the subsequent TRL level, and as evidenced by our discussion with Analog Devices, there is no guarantee that this will be consistent across components. One way to address this shortcoming is to explicitly assess the confidence to progress for each component, and weight the TRLs accordingly. Still, this shortcoming points to an area of further research -- are there more accurate measures of uncertainty that can be substituted for this calculation? How can we modify the current measure for likelihood to account for other factors that lead to uncertainty in technology development and integration?

Similarly, another challenge with this research is in selecting the correct measure for impact. We have presented a few options based on graph analysis, but we have not come across any empirical studies that help us choose the most accurate measure. Colombo (2016) published a statistical analysis of randomly generated architectures and change propagation indices that found network degree to be the best predictor of outgoing change risk (OCR) for components within a system. From the research, Colombo found that network degree had a 0.751 correlation with OCR, betweenness centrality with a correlation of 0.317 and closeness centrality with a correlation of 0.048. These data provide some evidence that degree is the most impactful measure on change propagation risk and further empirical research could provide more evidence for selecting degree, or a combination of measures, for predicting change propagation.

Finally, a key assumption in this research is that, should a change be required, all components require the same effort to change. However, some components are inherently more difficult to modify due to engineering complexity or other factors that don't have to do with interfaces or connectivity. For this research, we only considered severity of impact in the context of change propagation. Practitioners could choose to weight components according to their "effort to change" if the data is available, or they could forgo this direct assessment and rely on the experience and discussion of skilled engineers to bring up these observations as part of the risk decision process.

# 6 CONCLUSION

We propose a framework that follows traditional project management literature in defining risk as a combination of likelihood and impact. In our methodology, we choose likelihood to represent the probability that change will occur, and impact as the effects on the rest of the system, should a change be required. We select technology readiness levels as a measure for estimating likelihood due to its extensive documentation and widespread use within engineering industry. Given that change propagation occurs along interfaces, we propose that architectural attributes should be considered when estimating change propagation impacts. Some measures proposed within this research include nodal degree, closeness centrality, betweenness centrality, and information centrality. Empirical studies should be done to confirm the appropriateness of these measures and the circumstances under which they are best used.

We then present an industry example with data from a multinational semiconductor company. These data are analyzed together with team members from the company and the results are discussed. We calculate relative risk scores for each component and extend the calculation to interfaces between components. The data are presented through multiple visualizations and we discuss the merits of each. Finally, we find that the proposed framework provides a risk estimation that is in line with the experience of the engineers working on the project, and can be applied with relative ease.

#### REFERENCES

- ASDRE. (2011), "Technology Readiness Assessment (TRA) Guidance", US Department of Defense, Assistant Secretary of Defense for Research and Engineering, pp. 1–20.

- Borgatti, S.P. (2005), "Centrality and network flow", Social Networks, Vol. 27 No. 1, pp. 55-71.

- Brady, T.K. (2002), "Utilization of Dependency Structure Matrix Analysis to Assess Complex Project Designs", Volume 4: 14th International Conference on Design Theory and Methodology, Integrated Systems Design, and Engineering Design and Culture, ASME, p. 231.

- Clarkson, P.J., Simons, C. and Eckert, C. (2004), "Predicting Change Propagation in Complex Design", Journal of Mechanical Design, Vol. 126 No. 5, p. 788.

- Colombo, E.F. (2016), "Open Innovation Meets Changeability: Strategic Design Analyses for Cyberphysical Industry Platforms".

- Crawley, E., Cameron, B. and Selva, D. (2015), System Architecture: Strategy and Product Development for Complex Systems, Pearson Higher Education.

- Eppinger, S.D. and Browning, T.R. (2012), Design Structure Matrix Methods and Applications, The MIT Press.

Estrada, E., Fox, M., Higham, D.J. and Oppo, G.L. (2010), Network Science: Complexity in Nature and Technology, 1st ed., Springer-Verlag London, available at:https://doi.org/10.1007/978-1-84996-396-1

- Garg, T. (2017), Estimating Change Propagation Risk Using TRLs and System Architecture, Massachusetts Institute of Technology.

- Jimenez, H. and Mavris, D.N. (2014), "Characterization of Technology Integration Based on Technology Readiness Levels", Journal of Aircraft, Vol. 51 No. 1, pp. 291–302.

- NASA Office of the Chief Engineer. (2013), "NASA Systems Engineering Processes and Requirements", pp. 1–157.

- Olechowski, A., Eppinger, S.D. and Joglekar, N. (2015), "Technology readiness levels at 40: A study of state-ofthe-art use, challenges, and opportunities", Portland International Conference on Management of Engineering and Technology, Vol. September, pp. 2084–2094.

Project Management Institute. (2008), Project Management Body of Knowledge (PMBOK), Vol. 4.

- Sauser, B., Gove, R., Forbes, E. and Ramirez-marquez, J.E. (2010), "Integration maturity metrics : Development of an integration readiness level", Information Knowledge Systems Management, Vol. 9 No. 1, pp. 17–46.

- Segismundo, A. and Miguel, P.A.C. (2008), "Failure mode and effects analysis (FMEA) in the context of risk management in new product development: A case study in an automotive company", International Journal of Quality & Reliability Management, Vol. 25 No. 9, pp. 899–912.

- Terwiesch, C. and Loch, C.H. (1999), "Managing the process of engineering change orders: the case of the climate control system in automobile development", Journal of Product Innovation Management, Vol. 16 No. 2, pp. 160–172.

- United States Government Accountability Office. (2007), DEFENSE ACQUISITIONS Assessments of Selected Weapon Programs.